Ceci est le troisième versement de notre série de conception de CPU. Dans la première partie, nous avons abordé l'architecture informatique et le fonctionnement d'un processeur à un niveau élevé. La deuxième partie a examiné la manière dont certains composants individuels d’une puce ont été conçus et mis en œuvre. La troisième partie va encore plus loin pour voir comment les conceptions architecturales et schématiques sont transformées en puces physiques.

Comment transformer un tas de sable en processeur avancé? Découvrons-le.

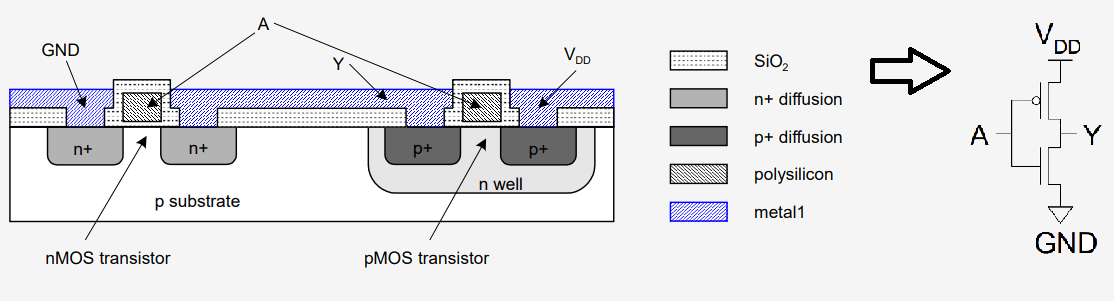

Comme nous l'avons vu précédemment, les processeurs et toutes les autres logiques numériques sont constitués de transistors. Un transistor est un commutateur à commande électronique que nous pouvons activer ou désactiver en appliquant ou en supprimant une tension de la grille. Nous avons expliqué qu'il existait deux types principaux de transistors: les dispositifs nMOS qui permettent le courant lorsque la porte est activée et les dispositifs pMOS qui permettent le courant lorsque la porte est désactivée. La structure de base d'un processeur dans lequel les transistors sont intégrés est en silicium. Le silicium est connu comme un semi-conducteur parce qu'il ne conduit pas complètement ou n'isole pas; c'est quelque part au milieu.

Pour transformer une plaquette de silicium en circuit utile en ajoutant des transistors, les ingénieurs de fabrication utilisent un processus appelé se doper. Le processus de dopage consiste à ajouter des impuretés soigneusement sélectionnées au substrat de silicium de base afin de modifier sa conductivité. Le but ici est de changer le comportement des électrons afin que nous puissions les contrôler. Tout comme il existe deux types de transistors, il existe deux types principaux de dopage correspondants.

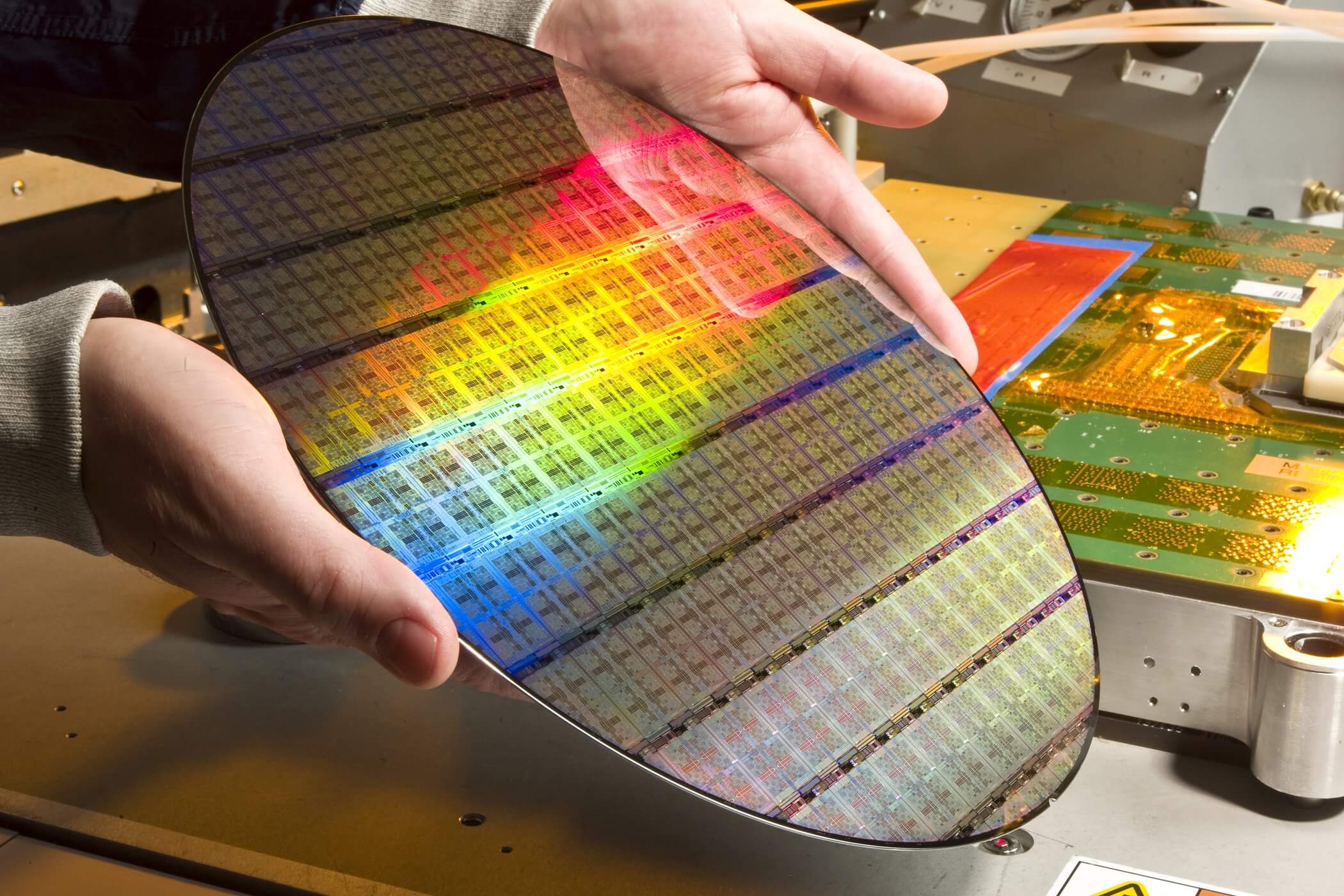

Le processus de fabrication d’une plaquette avant l’emballage des puces. Crédit photo: Evan Lissoos

Si nous ajoutons une quantité contrôlée d'éléments donneurs d'électrons tels que l'arsenic, l'antimoine ou le phosphore, nous pouvons créer une région de type n. Puisque la zone de silicium où ces éléments ont été appliqués a maintenant un excès d’électrons, elle se chargera négativement. C’est d’où le nom n-type et le «n» dans nMOS. En ajoutant au silicium des éléments accepteurs d'électrons tels que le bore, l'indium ou le gallium, nous pouvons créer une région de type p chargée positivement. C'est de là que vient le "p" dans p-type et pMOS. Les processus spécifiques pour ajouter ces impuretés au silicium sont connus sous le nom de Implantation ionique et La diffusion et ils sont un peu au-delà de la portée de cet article.

Maintenant que nous pouvons contrôler la conductivité électrique de certaines parties de notre silicium, nous pouvons combiner les propriétés de plusieurs régions pour créer des transistors. Les transistors utilisés dans les circuits intégrés, appelés MOSFET (Transistors à effet de champ à oxydes métalliques), possèdent quatre connexions. Le courant que nous contrôlons circule à travers la source et le drain. Dans un dispositif à canal n, il passe généralement dans le drain et sort de la source tandis que dans un dispositif à canal p, il circule généralement dans la source et dans le drain. La porte est le commutateur utilisé pour allumer et éteindre le transistor. Enfin, le corps de l'appareil ne concerne pas le processeur, nous n'en discuterons donc pas ici.

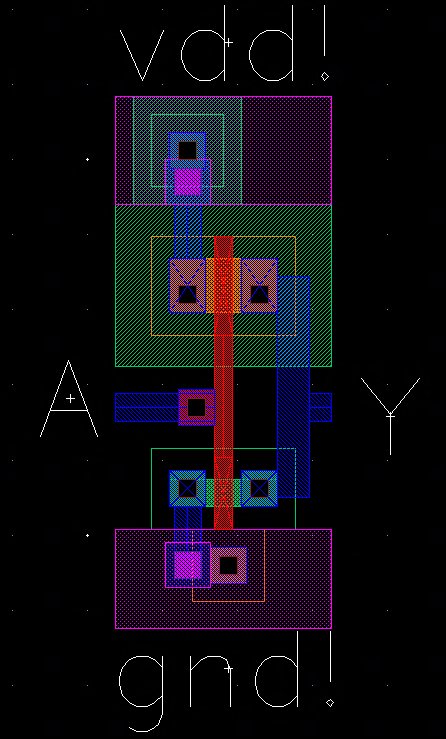

La structure physique d'un onduleur en silicium. Chaque région colorée a des propriétés de conductivité différentes. Notez comment les différents composants de silicium correspondent au schéma de droite

Les détails techniques du fonctionnement des transistors et de l'interaction des différentes régions sont suffisants pour remplir un cours de niveau universitaire supérieur. Nous allons donc aborder les bases. Une bonne analogie avec leur fonctionnement est un pont-levis sur une rivière. Les voitures, les électrons de notre transistor, voudraient se déplacer d’un côté à l’autre de la rivière, la source et le drain de notre transistor. En prenant comme exemple un périphérique nMOS, lorsque la porte n’est pas chargée, le pont-levis est levé, les électrons ne peuvent pas circuler sur le canal. Lorsque nous abaissons le pont-levis, nous formons une route sur la rivière et les voitures peuvent circuler librement. La même chose se passe dans un transistor. Le chargement de la porte forme un canal entre la source et le drain permettant au courant de circuler.

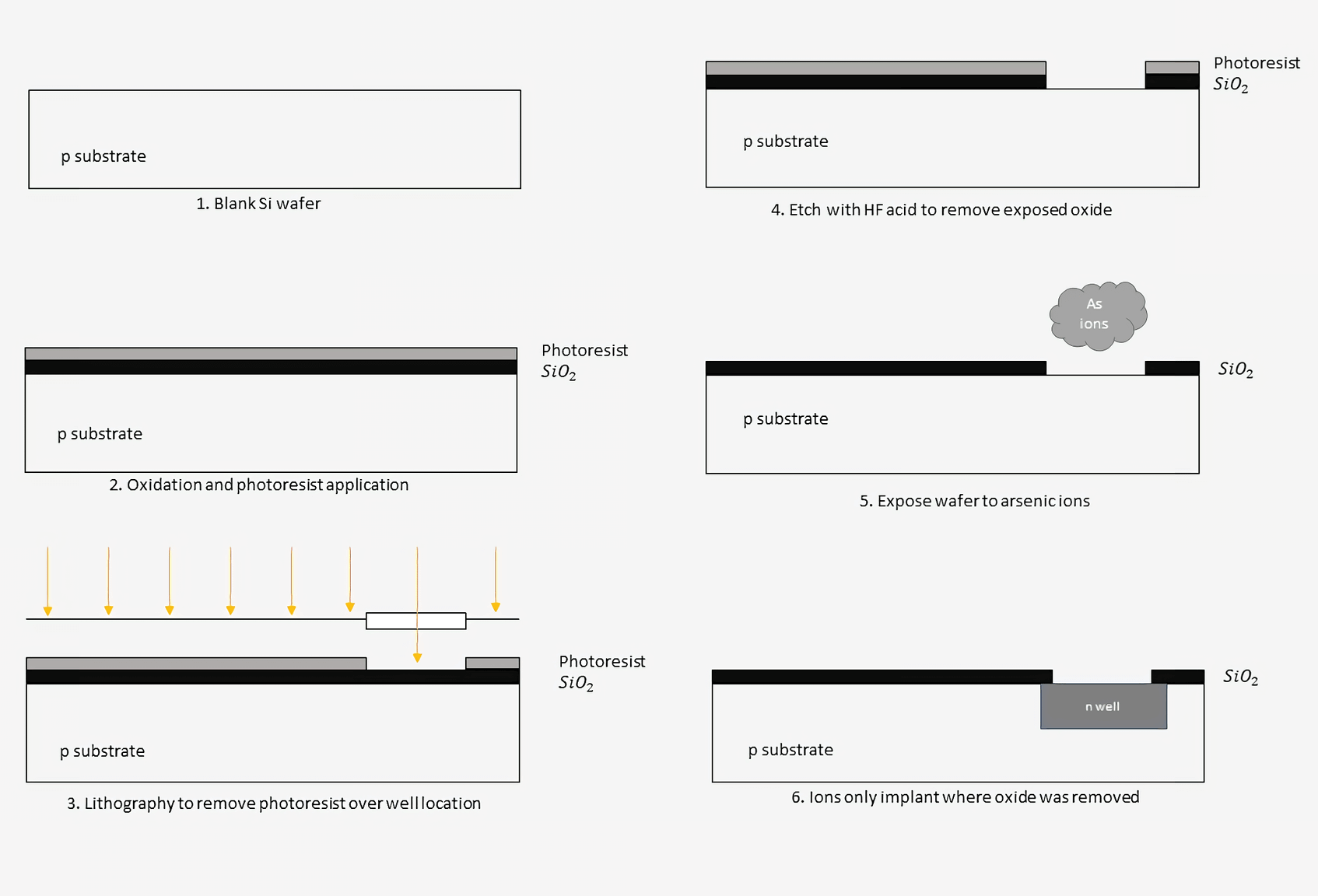

Pour pouvoir contrôler avec précision l'emplacement des différentes régions p et n du silicium, des fabricants tels qu'Intel et TSMC utilisent un processus appelé photolithographie. Il s'agit d'un processus extrêmement complexe en plusieurs étapes et les entreprises dépensent des milliards de dollars pour le perfectionner afin de pouvoir construire des transistors plus petits, plus rapides et plus efficaces en énergie. Imaginez une imprimante super précise pouvant être utilisée pour dessiner les motifs de chaque région sur le silicium.

Le processus de construction de transistors dans une puce commence par une tranche de silicium pure. Il est ensuite chauffé dans un four pour former une fine couche de dioxyde de silicium sur le dessus de la plaquette. Un polymère photosensible photosensible est ensuite appliqué sur le dioxyde de silicium. En projetant de la lumière à certaines fréquences sur la résine photosensible, nous pouvons la décaper dans les zones que nous souhaitons doper. Cette étape de la lithographie est similaire à celle utilisée par les imprimantes pour appliquer de l'encre sur certaines zones d'une page, mais à une échelle beaucoup plus petite.

La plaquette est attaquée avec de l'acide fluorhydrique pour dissoudre le dioxyde de silicium là où le photorésist a été éliminé. La résine photosensible est ensuite retirée, ne laissant que la couche d'oxyde en dessous. Les ions dopants peuvent ensuite être appliqués sur la tranche et ne s’implanteront que s’il existe des lacunes dans l’oxyde.

Ce processus de masquage, d’imagerie et de dopage est répété des dizaines de fois afin d’accumuler lentement chaque niveau de fonctionnalité dans un semi-conducteur. Une fois le niveau de silicium de base terminé, des connexions métalliques seront fabriquées sur le dessus pour connecter les différents transistors ensemble. Nous en parlerons un peu plus sur ces connexions et ces couches métalliques.

Bien entendu, les fabricants de puces ne font pas que créer des transistors un à un. Quand une nouvelle puce est conçue, ils vont générer des masques pour chaque étape du processus de fabrication. Ces masques contiendront les emplacements de chaque élément des milliards de transistors sur une puce. Plusieurs puces sont regroupées et fabriquées en une fois sur une seule matrice.

Une fois la plaquette fabriquée, les matrices individuelles sont tranchées et emballées. Selon la taille d'une puce, chaque tranche peut contenir des centaines ou plus de puces. En règle générale, plus la puce produite est puissante, plus la matrice sera grande et moins le fabricant pourra puiser de puces dans chaque tranche.

Il est facile de penser que nous devrions simplement créer d’énormes puces super puissantes avec des centaines de cœurs, mais cela n’est pas possible. Actuellement, le principal facteur qui nous empêche de fabriquer des puces de plus en plus grosses est le défaut de fabrication. Les puces modernes ont des milliards de transistors et si une seule partie de celle-ci est cassée, il faudra peut-être tout jeter. À mesure que nous augmentons la taille des processeurs, le risque qu'une puce soit défectueuse augmente.

Les rendements réels que les entreprises tirent de leurs processus de fabrication sont des secrets bien gardés, mais une estimation de 70% à 90% est bonne. Il est courant que les entreprises sur-conçoivent leurs puces avec des fonctionnalités supplémentaires, sachant que certaines pièces ne fonctionneront pas. Par exemple, Intel peut concevoir une puce à 8 cœurs mais ne la vendre que sous forme de puce à 6 cœurs, car ils estiment qu'un ou deux cœurs peuvent être brisés. Les puces présentant un nombre inhabituellement faible de défauts sont généralement réservées pour être vendues à un prix plus élevé dans un processus appelé binning.

L'un des principaux termes marketing associés à la fabrication de puces est la taille de la fonctionnalité. Par exemple, Intel travaille sur un processus de 10 nm, AMD utilise un processus de 7 nm pour certains GPU et TSMC a commencé à travailler sur un processus de 5 nm. Que signifient tous ces chiffres? Traditionnellement, la taille de la caractéristique représente la largeur minimale entre le drain et la source d'un transistor. La technologie ayant évolué, nous avons pu réduire la taille de nos transistors pour pouvoir en installer de plus en plus sur une seule puce. À mesure que les transistors deviennent plus petits, ils deviennent également de plus en plus rapides.

Lorsque l'on regarde ces chiffres, il est important de noter que certaines entreprises peuvent baser la taille de leur processus sur des dimensions différentes de celles de la largeur standard. Cela signifie que des processus de tailles différentes d'entreprises différentes peuvent en réalité aboutir au même transistor de taille. D'autre part, tous les transistors d'un processus donné n'ont pas non plus la même taille. Les concepteurs peuvent choisir de rendre certains transistors plus grands que d'autres en fonction de certains compromis. Pour un processus de conception donné, un transistor plus petit sera plus rapide puisqu'il faut moins de temps pour charger et décharger la grille. Cependant, les transistors plus petits ne peuvent piloter qu'un très petit nombre de sorties. Si un élément particulier de la logique doit générer quelque chose qui nécessite beaucoup de puissance, tel qu'une broche de sortie, il faudra le rendre beaucoup plus gros. Ces transistors de sortie peuvent avoir des ordres de grandeur plus grands que les transistors à logique interne.

Un coup de matrice d'un processeur AMD Zen récent. Plusieurs milliards de transistors composent cette conception.

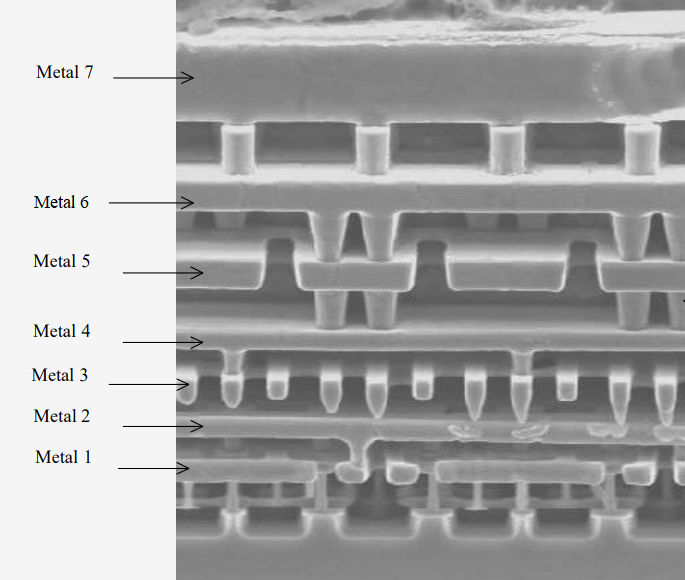

La conception et la construction des transistors ne représentent cependant que la moitié de la puce. Nous devons construire des câbles pour tout connecter conformément au schéma. Ces connexions sont réalisées à l'aide de couches métalliques situées au-dessus des transistors. Imaginez un échangeur autoroutier à plusieurs niveaux avec des rampes d'accès, des bretelles d'accès et différentes routes qui se croisent. C'est exactement ce qui se passe à l'intérieur d'une puce, bien qu'à une échelle beaucoup plus petite. Différents processus auront différents nombres de couches d'interconnexion métalliques au-dessus des transistors. Au fur et à mesure que les transistors deviennent plus petits, il faut davantage de couches métalliques pour pouvoir router tous les signaux. Le processus à 5 nm à venir du TMSC comprend 15 couches de métal. Imaginez un échangeur autoroutier vertical sur 15 niveaux, qui vous permettra de comprendre à quel point l’acheminement est complexe à l’intérieur d’une puce.

L'image du microscope ci-dessous montre le réseau formé par sept couches métalliques. Chaque couche est plate et à mesure qu'elle monte, les couches grossissent pour aider à réduire la résistance. Entre chaque couche se trouvent de petits cylindres métalliques appelés vias utilisés pour sauter d'une couche supérieure. Chaque couche alterne généralement dans le sens opposé de celle située en dessous pour aider à réduire les capacités indésirables. Les couches métalliques impaires peuvent être utilisées pour établir des connexions horizontales, tandis que les couches paires peuvent être utilisées pour établir des connexions verticales.

Comme vous pouvez l’imaginer, tous ces signaux et couches métalliques deviennent extrêmement difficiles à gérer très rapidement. Pour résoudre ce problème, des programmes informatiques sont utilisés pour placer et router automatiquement les transistors. En fonction de l'état d'avancement de la conception, les programmes peuvent même convertir des fonctions en code C de haut niveau jusqu'aux emplacements physiques de chaque fil et transistor. En règle générale, les fabricants de puces laissent les ordinateurs générer automatiquement la plupart de la conception, puis ils analysent et optimisent manuellement certaines sections critiques.

Lorsque les entreprises souhaitent construire une nouvelle puce, elles commencent leur conception avec des cellules standard fournies par la société de fabrication. Par exemple, Intel ou TSMC fourniront aux concepteurs des composants de base tels que des portes logiques ou des cellules de mémoire. Les concepteurs peuvent ensuite combiner ces cellules standard dans la puce qu’ils souhaitent construire. Ils enverront ensuite la fonderie, l'endroit où le silicium brut est transformé en puces fonctionnelles, les dispositions des transistors et des couches métalliques de la puce. Ces mises en page sont transformées en masques utilisés dans le processus de fabrication décrit ci-dessus. Nous verrons ensuite à quoi ce processus de conception pourrait ressembler pour une puce extrêmement basique.

Nous voyons d’abord la structure d’un onduleur qui est une cellule standard. Le rectangle vert barré en haut est le transistor pMOS et le rectangle vert transparent en bas est le transistor nMOS. Le fil rouge vertical correspond à la porte en silicium polycristallin, les zones bleues au métal 1 et les régions mauves au métal 2. L'entrée A entre à gauche et la sortie Y à droite. Les connexions d’alimentation et de mise à la terre sont effectuées en haut et en bas sur le métal 2.

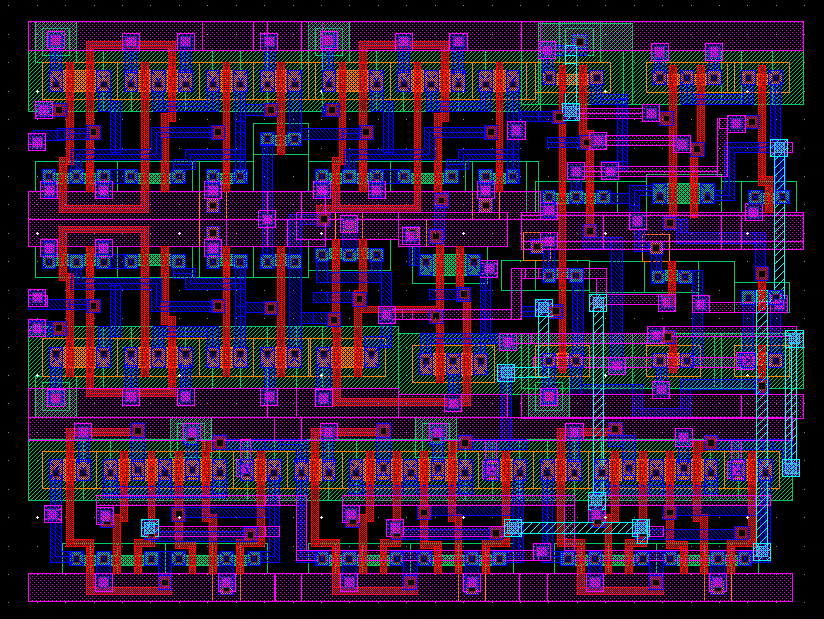

En combinant plusieurs portes, nous avons ici une unité arithmétique à 1 bit de base. Cette conception peut ajouter, soustraire et effectuer des opérations logiques sur deux entrées de 1 bit. Les fils bleus barrés qui vont verticalement sont en métal à 3 couches. Les carrés légèrement plus grands aux extrémités des fils sont des vias qui connectent deux couches.

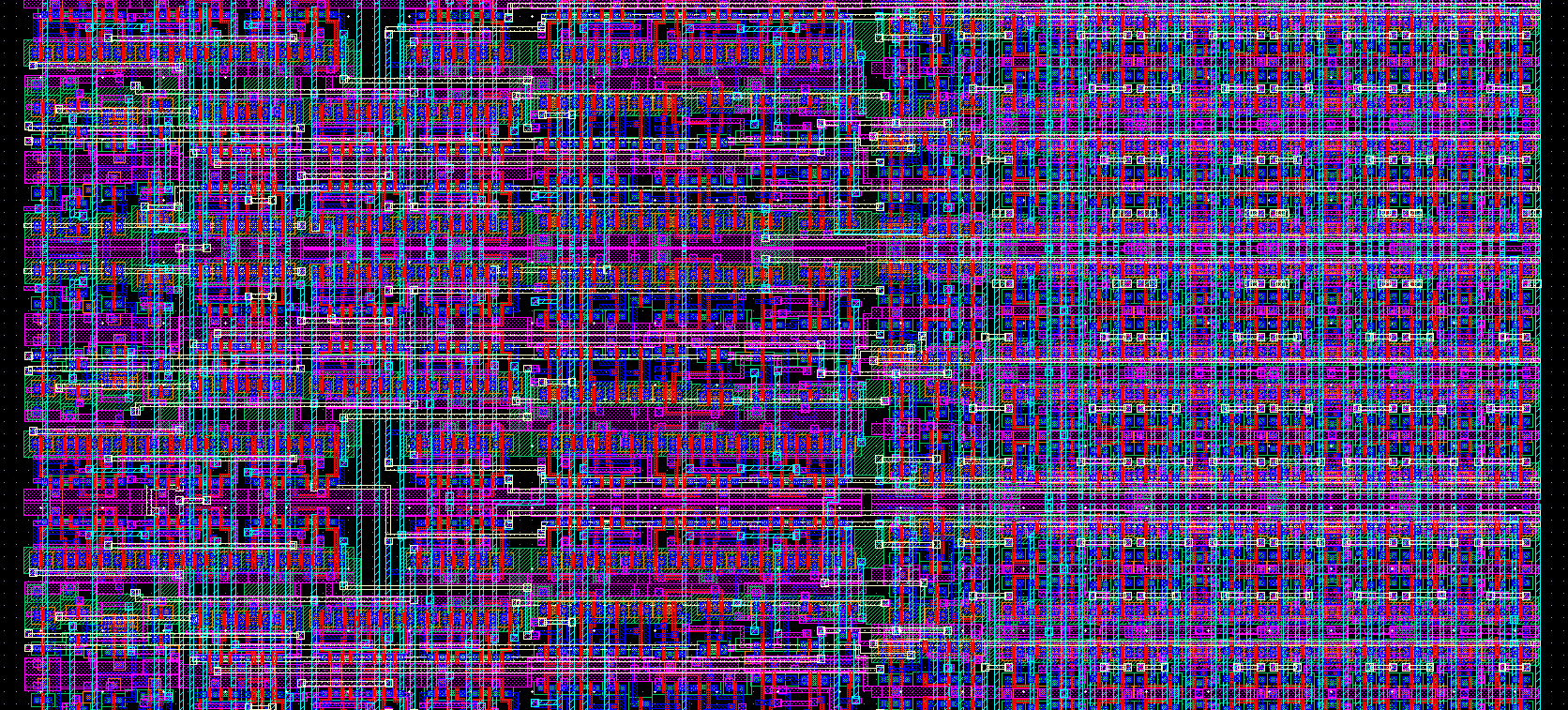

Enfin, réunissant plusieurs cellules et environ 2 000 transistors, nous disposons d’un processeur de base à 4 bits avec 8 octets de RAM sur quatre couches métalliques. Considérant la complexité de cette opération, on ne peut qu'imaginer la difficulté de concevoir un processeur 64 bits avec des mégaoctets de cache, plusieurs cœurs et plus de 20 étapes de pipeline. Étant donné que les processeurs hautes performances actuels peuvent avoir plus de 5 à 10 milliards de transistors et une douzaine de couches métalliques, il n’est pas exagéré de dire qu’ils sont littéralement des millions de fois plus complexes que cela.

Cela devrait vous permettre de comprendre pourquoi votre nouveau processeur est une technologie coûteuse ou pourquoi il faut tant de temps à AMD et à Intel entre les versions du produit. Il faut généralement entre 3 et 5 ans pour qu'une nouvelle puce passe de la planche à dessin au marché. Cela signifie que les puces les plus rapides d'aujourd'hui sont fabriquées avec une technologie vieille de plusieurs années et que nous ne verrons pas de puces avec la technologie de fabrication de pointe d'aujourd'hui avant de nombreuses années.

Avec cela, nous en avons tous terminé avec notre plongée dans la façon dont les processeurs sont construits.

Dans le quatrième et dernier volet de la série, nous allons revenir du domaine physique et examiner les tendances actuelles du secteur. Sur quoi les chercheurs travaillent-ils maintenant pour rendre la prochaine génération d'ordinateurs encore plus rapide?

Dans la troisième partie de la série, nous avons exploré le fonctionnement physique des transistors, la manière dont leurs composants individuels sont construits en silicium et la manière dont ils sont connectés pour créer des circuits et des puces utiles.

Crédit Masthead: Image de fabrication de semi-conducteurs par Macro